In the semiconductor world of 2026, designing a System on Chip (SoC) is an incredible feat of engineering. We are no longer just putting a few processors and memory blocks together. A modern SoC is a city of billions of transistors, housing specialized AI engines, complex communication fabrics, and layers of security protocols. However, there is a hard truth that every B.Tech student must realize: designing the chip is often the easy part. Verifying that it actually works is where the real battle begins.

Currently, verification consumes nearly 70% of the total design cycle. If a bug escapes into the final silicon at a 2nm or 3nm node, the cost of a “re-spin” can exceed twenty million dollars. To avoid such a disaster, engineers must navigate a maze of increasingly difficult challenges.

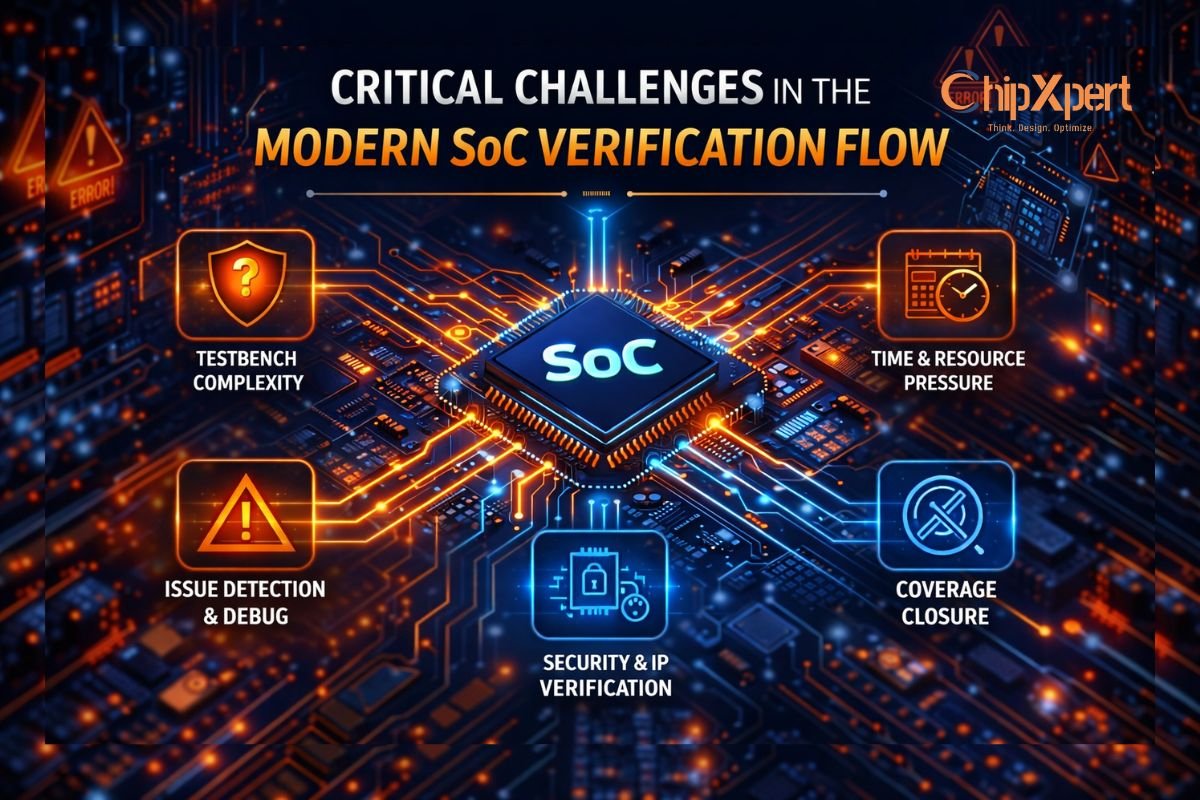

1. The Explosion of State Space Complexity

The primary challenge in 2026 is the sheer scale of the “state space.” An SoC with multiple CPU cores, dozens of peripheral IPs, and a high-speed interconnect has an almost infinite number of possible operational states. Testing every single combination of inputs and events is mathematically impossible.

Traditional simulation-based testing cannot keep up. This is why the industry has shifted heavily toward Constrained Random Verification (CRV) using SystemVerilog and UVM. The challenge for a verification engineer is not just writing tests, but writing “smart” constraints that can guide the simulator into the dark, unexplored corners of the design where the most dangerous bugs hide.

2. The Hardware-Software Integration Gap

An SoC is useless without its software stack. In the past, hardware was verified first, and software was written later. In 2026, this “serial” approach is a recipe for failure. The challenge is ensuring that the hardware and software interact perfectly before the first chip is even manufactured.

Hardware-Software Co-verification requires massive computational power. Engineers must use hardware emulators and FPGAs to run the actual boot code and drivers against the RTL design. Debugging a software hang that is caused by a subtle hardware timing glitch is one of the most difficult tasks in the entire VLSI flow. At ChipXpert, we emphasize this “system-level” thinking, teaching students how to bridge the gap between low-level gates and high-level firmware.

3. Maintaining Performance and Latency Requirements

Verification is no longer just about “Is the output correct?” In 2026, we are equally concerned with “Is the output on time?” For AI accelerators and autonomous driving chips, a latency spike of a few microseconds can be a catastrophic failure.

Verifying performance across a complex Network-on-Chip (NoC) is a massive hurdle. You have to ensure that under “heavy traffic” conditions, a critical data packet from a sensor reaches the processor without being blocked by a low-priority background task. Creating these realistic “traffic scenarios” in a testbench requires a deep understanding of bus protocols like AXI, CHI, and UCIe.

4. The Rising Threshold of Security Verification

As chips become more connected, they become more vulnerable. In 2026, “Security Verification” has become a standalone discipline. Engineers must now verify that there are no “side channels” where a hacker could steal cryptographic keys by measuring power consumption or electromagnetic emissions.

Verifying “Data Isolation” is another huge challenge. You have to prove that a non-secure app running on the SoC can never, under any circumstances, access the secure memory region used by the fingerprint scanner or the payment engine. This requires formal verification methods where mathematical proofs are used to guarantee that certain “illegal” states can never be reached.

5. Achieving Functional Coverage Closure

The final and perhaps most frustrating challenge is knowing when to stop. In verification, “100% Code Coverage” is a basic requirement, but it doesn’t mean the chip is bug-free. The real goal is “Functional Coverage Closure.”

This involves mapping every line of the architectural specification to a specific “coverpoint” in the testbench. Achieving 100% functional coverage in a 2026 SoC is a grueling process of analyzing reports, identifying “coverage holes,” and writing targeted tests to fill them. It is a game of diminishing returns where the last 1% of coverage often takes as much effort as the first 90%.

Conclusion: Why Verification is the Career of the Future

If these challenges sound daunting, it is because they are. But for a B.Tech student, these hurdles represent an incredible career opportunity. The semiconductor industry is currently facing a massive shortage of “Verification Architects”—engineers who don’t just know the syntax of a language, but who understand the entire SoC ecosystem.

At ChipXpert, we train you to tackle these real-world problems head-on. By mastering advanced UVM environments, performance modeling, and formal verification, you move from being a “tester” to being a “guardian of quality.” The SoC verification flow is the most challenging part of silicon design, but it is also the most rewarding. In the era of 2nm AI silicon, the engineer who can prove the design is correct is the most valuable person in the room.

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.