In the world of VLSI (Very-Large-Scale Integration) design, validation and verification are as important as design itself. Among the key verification steps, gate-level simulation plays a critical role in ensuring the logical correctness and timing behavior of a digital design before it goes into silicon.

Whether you’re preparing for industry certification, planning a career in chip design, or managing a digital design project, understanding gate-level simulation helps you catch issues early, optimize performance, and improve design reliability.

In this article, we’ll break down what gate-level simulation is, why it matters, how it works, and how it fits into the overall design and verification flow.

What Is Gate-Level Simulation?

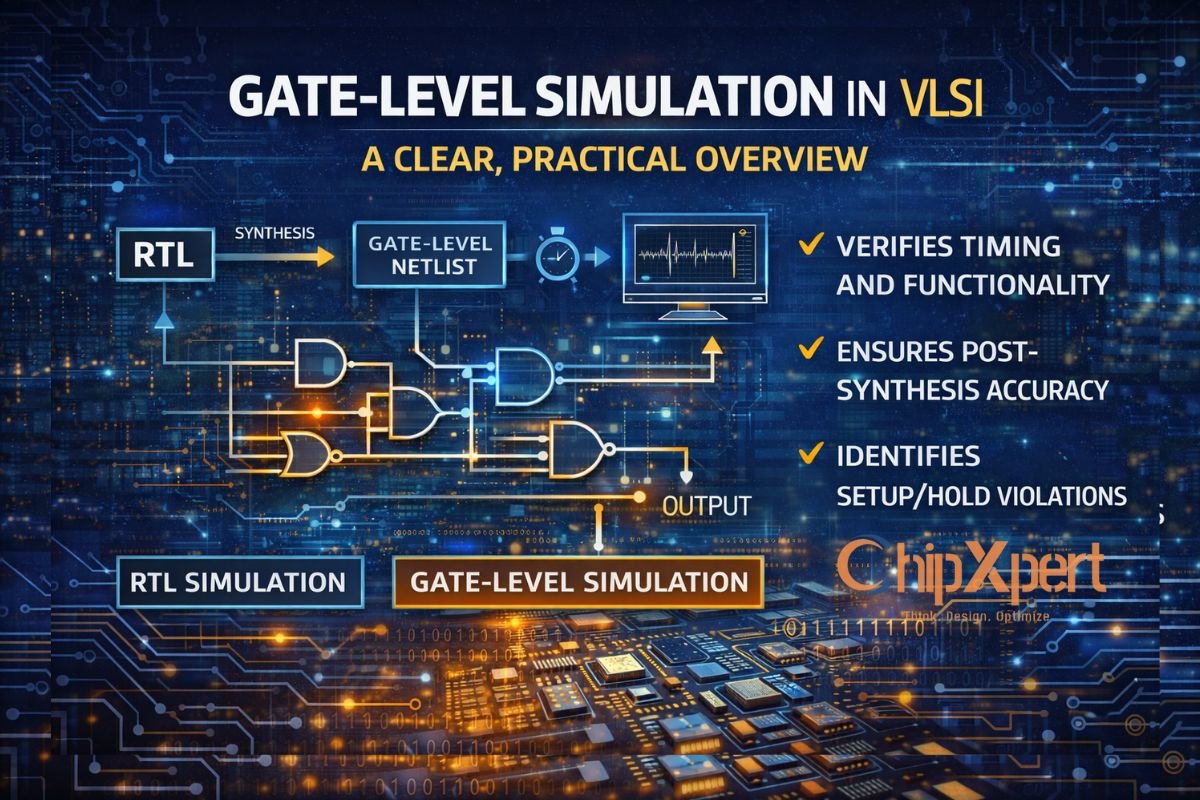

At its essence, gate-level simulation refers to simulating a digital circuit after synthesis, using a netlist that represents the design in terms of logic gates (such as AND, OR, NOT, flip-flops) instead of high-level code like Verilog or VHDL.

This simulation includes:

- Logical behavior of gates and flip-flops

- Propagation delays extracted from synthesis or post-layout timing

- Timing interactions between elements

Unlike RTL (Register-Transfer Level) simulation that only verifies logic correctness, gate-level simulation verifies how the actual synthesized design behaves, including timing and delay effects.

Why Gate-Level Simulation Matters

1. Timing Accuracy

Once a design is synthesized, the logic is converted into a network of basic gates and flip-flops. Gate-level simulation incorporates timing delays extracted from the synthesis or place-and-route tool. This enables verification of whether signals arrive at the right time and whether setup or hold violations occur.

2. Verification of Real Design Behavior

At the RTL level, simulation doesn’t reflect how logic synthesis reshapes the design. Gate-level simulation verifies the actual implementation, catching issues that RTL simulation might miss, such as unintended hazards, glitches due to timing delay, or missing clocks.

3. Confidence Before Hardware Testing

Verifying behavior at the gate level increases confidence that the design will function correctly in hardware. Finding bugs early avoids costly iterations after fabrication.

Gate-Level Simulation vs. RTL Simulation

To understand the importance of gate-level simulation, it helps to contrast it with RTL simulation:

| Feature | RTL Simulation | Gate-Level Simulation |

| Level of abstraction | High | Low |

| Timing delays | Ignored | Included |

| Logic view | Behavioral | Structural (gates) |

| Verification goal | Functional correctness | Timing & functional correctness |

| Speed | Faster | Slower |

RTL simulation is typically used earlier in development for functional validation. Gate-level simulation is used later, after synthesis or place-and-route, to verify timing effects and real implementation behavior.

How Gate-Level Simulation Works

Here is a simplified step-by-step breakdown of the process:

1. Synthesis Output

The design written in HDL (Verilog/VHDL) is synthesized into a gate-level netlist. This netlist represents the design using primitive gates and flip-flops.

2. Timing Annotation

Timing information (like propagation delays, setup/hold timing) is extracted using Static Timing Analysis tools and annotated back into the netlist.

3. Testbench Execution

A testbench often the same used in RTL simulation is applied to the gate-level design. Input vectors are driven through this netlist to observe outputs.

4. Result Analysis

Simulation outputs are compared with expected outputs to ensure the design behaves as intended. Timing violations or unexpected behaviors are identified and debugged.

When to Use Gate-Level Simulation

Gate-level simulation is typically performed at these stages:

After RTL Functional Verification

Once the design logic is verified functionally, gate-level simulation confirms that the synthesized netlist still represents correct behavior with timing delays.

After Place-and-Route

Once physical layout is completed, gate-level simulation with post-layout timing enables verification of real routing and cell delays.

Before Tape-Out

This final check ensures a higher degree of confidence before the design is sent for fabrication.

Challenges of Gate-Level Simulation

While gate-level simulation is powerful, it also comes with challenges:

1. Slower Simulation Speed

Because the simulation includes detailed gate-level behavior and timing delays, it runs noticeably slower than RTL simulation.

2. Resource Intensity

Large designs with millions of gates require significant computational resources for simulation.

3. Testbench Compatibility

The testbench must be robust and comprehensive to catch corner cases at the gate level weak test vectors may miss critical issues.

Despite these challenges, gate-level simulation remains a cornerstone of reliable verification.

Best Practices for Effective Gate-Level Simulation

Use Optimized Test Vectors

Gate-level simulation is slow, so use targeted, high-coverage test vectors that focus on timing-critical functionality.

Correlate RTL and Gate-Level Results

Verify that outputs from gate-level simulation match RTL results for the same inputs. This correlation ensures that synthesis did not alter functionality.

Perform Post-Layout Timing Simulation

Incorporate accurate delays from the physical layout for final validation.

Analyze Signal Glitches

Since timing effects can cause hazards or glitches, examine waveforms for unexpected transitions that didn’t occur in RTL.

Conclusion: Gate-Level Simulation: A Key to Reliable Chips

In a world where chips are expected to operate at high performance with zero defects, gate-level simulation stands out as a critical step in the verification process. It bridges the gap between abstract logic and real implementation with timing accuracy, giving designers confidence that their creations will work as intended.

Whether you’re starting out or already working in VLSI design, mastering gate-level simulation empowers you to deliver more robust, reliable, and silicon-ready designs.

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.