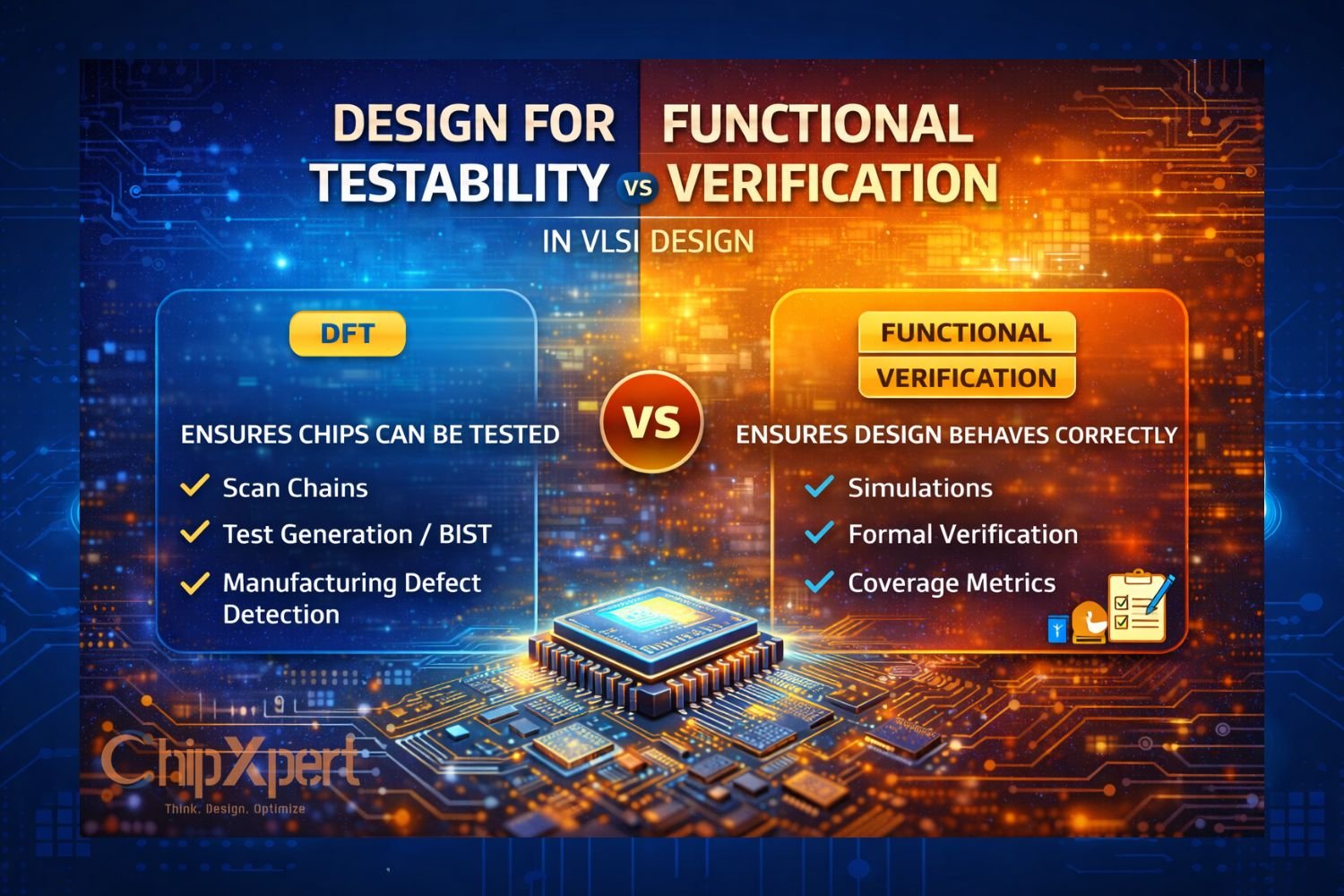

In modern VLSI (Very Large Scale Integration) design, ensuring that a chip functions correctly and is reliably testable are both essential parts of building successful silicon. Two important processes involved in this journey — Design for Testability (DFT) and Functional Verification, may seem similar at first glance, but they serve very different purposes.

In this article, we’ll break down the core differences between DFT and functional verification, and explain how they complement each other to make chips both reliable and production-ready.

What Is Functional Verification?

At its heart, functional verification is all about correctness. It determines whether a design works exactly as intended according to its specification.

When engineers write the logic for a chip in HDL (like Verilog or SystemVerilog), they must confirm that this logic performs the right operations, for example, whether an adder truly adds two numbers, or whether a controller correctly sequences events.

Functional verification typically involves activities like:

- Simulating the design with hundreds of test cases

- Writing assertions to check specific conditions

- Using formal methods to mathematically prove correctness

- Tracking coverage to ensure every part of the design has been tested

The goal is to find and eliminate bugs before the chip goes through synthesis and manufacturing.

What Is Design for Testability (DFT)?

Design for Testability (DFT), on the other hand, focuses on how well a manufactured chip can be tested.

Even if a design is correct in simulation, once the chip is fabricated, manufacturing defects like shorted wires or stuck-at faults may occur. DFT ensures that these defects can be detected efficiently in high-volume testing.

Rather than checking functional correctness (as verification does), DFT improves the structural testability of a design by adding features such as:

- Scan chains that allow internal flip-flops to be controlled and observed

- Test access mechanisms that simplify applying test patterns

- Built-In Self-Test (BIST) blocks for autonomous testing

- Automatic test pattern generation support

These features make post-manufacturing tests faster, more thorough, and more cost-effective.

Core Differences Between DFT and Functional Verification

Though both are crucial to chip success, DFT and functional verification differ in their main objectives, techniques, and timing in the design flow:

1. Objective

- Functional verification ensures that the logical behavior of the design matches the specification.

- DFT ensures that once the chip is fabricated, it can be thoroughly tested for manufacturing defects.

2. Timing in the Design Flow

- Functional verification begins early, usually as soon as the RTL design is ready, and continues through synthesis and gate-level simulation.

- DFT often starts after RTL design reaches maturity, especially during or after synthesis, when test structures are inserted into the design.

3. Output Focus

- Verification outputs a bug-free logical design toward tape-out.

- DFT outputs a design that includes additional test logic to be used during mass production testing.

4. Common Techniques

- Verification uses simulations, formal verification, and coverage metrics to validate behavior.

- DFT uses hardware test structures, scan logic, and test pattern generation to probe internal components.

Why Both Are Important

Understanding both DFT and functional verification is vital for developing reliable, high-quality chips.

Functional Verification Ensures Correct Logic

Without functional verification, a chip could be fabricated with logic errors that lead to incorrect behavior — something that could be extremely costly when discovered after manufacturing.

DFT Ensures Detectability of Manufacturing Defects

Even if a design is functionally perfect, physical manufacturing defects can still render chips unusable if there’s no easy way to detect them. DFT ensures these defects don’t go unnoticed during testing.

How DFT and Functional Verification Work Together

Rather than competing, DFT and functional verification complement each other:

- Functional verification ensures the design works as intended.

- DFT ensures the design can be tested efficiently after manufacturing.

For example, a verification engineer may confirm that a logic block behaves correctly. A DFT engineer then ensures that the same block includes structures that allow faults to be detected in that logic after the chip is built.

Collaborating early in the flow, especially during RTL development, helps ensure that verification and testability goals align, resulting in both a correct and testable design.

Practical Scenarios: How They Differ in Action

Scenario 1: Functional Bug

If a counter doesn’t rollover correctly in simulation, that’s a functional issue. Verification tools catch it, and the designer fixes the RTL or logic behavior.

Scenario 2: Manufacturing Defect

If after fabrication, a connection inside a chip is shorted due to process variation, verification alone won’t catch this, because it only checks logical behavior pre-fabrication. DFT structures allow test equipment to detect this fault on every manufactured chip.

These examples show why both disciplines are necessary for successful chip production.

Final Thoughts

In the complex world of VLSI, functional verification and Design for Testability are two distinct but deeply interconnected processes. Verification ensures the design behaves as specified, while DFT ensures it can be tested thoroughly and efficiently after manufacturing.

Modern chip success relies on mastering both, functional correctness and testability, to produce high-quality, reliable silicon that performs well in the field and can be manufactured at scale.

Understanding the differences between DFT and functional verification empowers engineers to create better designs, find bugs earlier, and deliver chips that succeed not just in simulation, but in real-world use.

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.