In modern semiconductor manufacturing, designing a chip is far more complex than simply connecting transistors together. As integrated circuits continue to shrink to advanced technology nodes, engineers must follow strict guidelines to ensure that the final design can be manufactured reliably. These guidelines are known as layout design rules.

Layout design rules play a crucial role in VLSI physical design because they define the constraints that engineers must follow while placing and routing circuit elements. Without these rules, it would be extremely difficult to produce chips that function correctly and maintain high manufacturing yield.

In this article, we explore what layout design rules are, why they are important, and how they influence chip design in the modern semiconductor industry.

Understanding Layout Design Rules in VLSI

Layout design rules are a set of geometric and spacing constraints that guide engineers when creating the physical layout of integrated circuits. These rules define the minimum dimensions and distances between various components such as transistors, wires, and contacts.

The primary purpose of these rules is to ensure that the chip layout can be manufactured accurately using semiconductor fabrication processes. Since fabrication involves extremely precise lithography and etching steps, even a small violation of design rules can lead to defects or nonfunctional chips.

By following layout design rules, designers ensure that the final layout is compatible with the manufacturing process used by semiconductor foundries.

Why Layout Design Rules Are Important

Layout design rules serve multiple purposes in chip design and manufacturing. They help maintain the balance between design complexity and manufacturability.

Ensuring Manufacturing Reliability

Semiconductor fabrication processes require strict tolerances. Layout rules define safe distances and dimensions that prevent short circuits, open circuits, and other defects during manufacturing.

Improving Yield

Yield refers to the percentage of functional chips produced from a wafer. Designs that follow layout rules closely are more likely to be manufactured successfully, which improves production yield.

Maintaining Electrical Performance

Proper spacing and routing defined by design rules help reduce unwanted electrical effects such as parasitic capacitance and signal interference.

Preventing Physical Defects

Design rules prevent issues such as overlapping metal layers, insufficient spacing between wires, or incorrect transistor dimensions that could damage the chip structure.

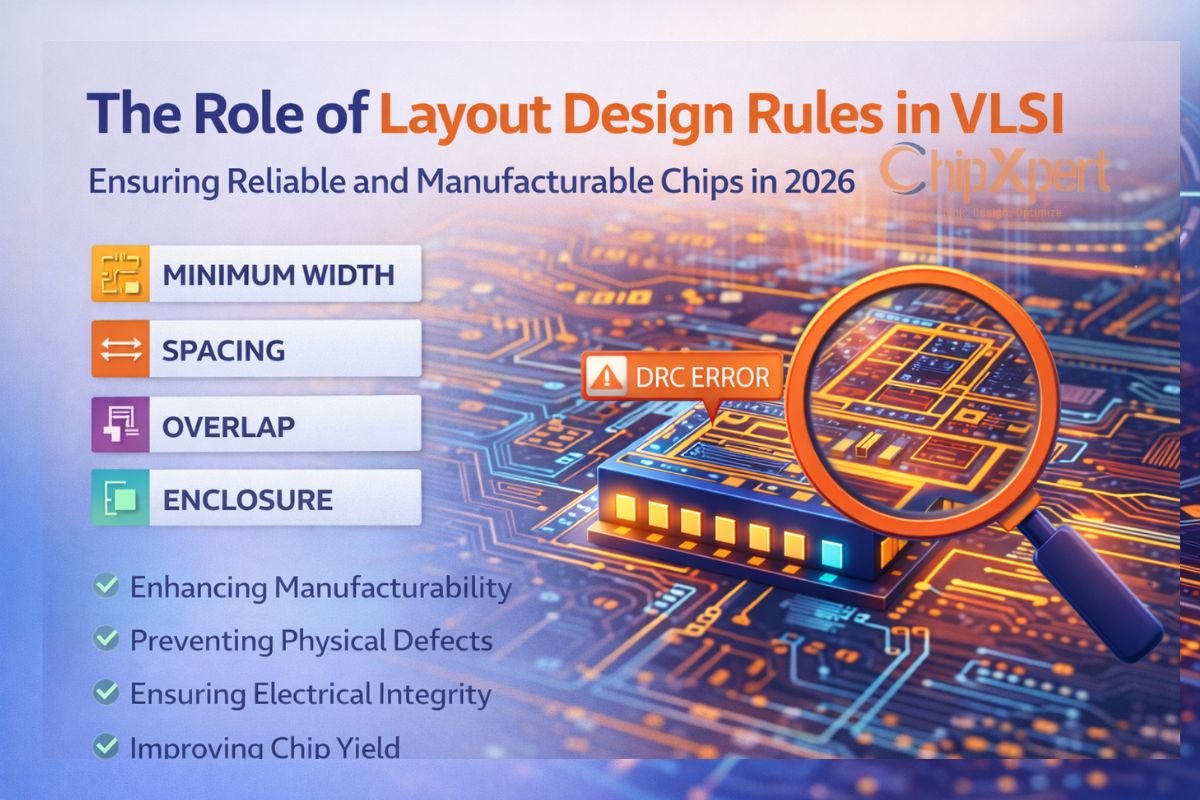

Types of Layout Design Rules

Layout design rules cover many aspects of the chip layout. Some of the most important rule categories include the following.

Minimum Width Rules

Minimum width rules specify the smallest allowable width for wires, diffusion regions, or polysilicon structures. Maintaining the required width ensures that these elements can be reliably manufactured.

Spacing Rules

Spacing rules define the minimum distance between two components on the same layer. Proper spacing prevents electrical shorts and manufacturing defects.

Overlap Rules

Overlap rules specify how different layers must overlap to ensure proper electrical connections between components.

Enclosure Rules

Enclosure rules define how one layer must surround another layer, such as how metal layers must cover contact points.

These rules ensure that different elements of the chip layout connect correctly and maintain structural integrity.

Layout Design Rules in the Physical Design Flow

Layout rules are enforced throughout the physical design stage of VLSI development. During layout creation, designers use specialized Electronic Design Automation tools to ensure that the layout follows all required constraints.

One important step in this process is Design Rule Checking (DRC). DRC tools automatically analyze the layout and identify any rule violations. Engineers must fix these violations before the design can proceed to manufacturing.

Design rule checking is essential because even a single violation may cause fabrication failure or reliability issues.

Impact of Layout Design Rules on Advanced Nodes

In modern semiconductor nodes such as 5nm, 3nm, and beyond, layout design rules have become increasingly complex. As transistor sizes shrink, maintaining proper spacing and alignment becomes more challenging.

Advanced nodes often require:

- Multiple patterning techniques

- Complex routing strategies

- Strict layer alignment rules

- Advanced verification processes

These constraints make layout design more demanding but also help ensure that high-performance chips can be manufactured successfully.

Challenges Engineers Face with Layout Rules

While layout design rules are necessary, they also introduce certain challenges for chip designers.

Increased Design Complexity

Modern chips contain billions of transistors, making it difficult to manage all rule constraints manually.

Performance Trade-offs

Following strict spacing and routing rules sometimes forces designers to adjust layouts in ways that may impact performance or area.

Tool Dependency

Designers rely heavily on advanced design tools to check and enforce layout rules, making tool expertise an essential skill for VLSI engineers.

Despite these challenges, layout rules remain fundamental to reliable chip manufacturing.

The Future of Layout Design Rules in 2026 and Beyond

As semiconductor technology evolves, layout design rules will continue to become more sophisticated. Emerging technologies such as chiplet architectures, 3D stacking, and advanced packaging introduce new layout challenges that require updated rule sets.

Artificial intelligence is also being integrated into design automation tools to help engineers optimize layouts while automatically complying with complex rule constraints.

These innovations are expected to improve design productivity while maintaining strict manufacturing standards.

Conclusion

Layout design rules are an essential part of VLSI physical design, ensuring that chip layouts are manufacturable, reliable, and electrically stable. By defining constraints on spacing, dimensions, and layer interactions, these rules help engineers avoid defects and improve manufacturing yield.

As semiconductor technology continues advancing into smaller nodes and more complex architectures, the importance of layout design rules will only grow. Engineers who understand and apply these rules effectively play a key role in delivering reliable and high-performance integrated circuits.

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.