In modern semiconductor design, delivering a chip that works reliably from prototype to production isn’t just about good circuit design, it’s about testability. That’s where Design for Testability (DFT) plays a pivotal role.

DFT ensures that a chip is not only functional but also verifiable and manufacturable in large volumes. Without robust DFT strategies, even well-designed logic could fail in real-world testing, causing costly delays or product failures.

In this article, we’ll explore what DFT is, why it matters throughout the chip life cycle, and how it enhances manufacturing quality while reducing time-to-market.

What Is DFT and Why Is It Crucial?

Design for Testability (DFT) refers to a set of methodologies and circuit modifications that make integrated circuits easier to test during manufacturing and validation.

Without DFT, testing every possible state of a complex chip would be nearly impossible. Modern chips contain millions, sometimes billions of transistors. Exhaustively testing all functional scenarios through external signals alone would take impractical amounts of time and resources.

DFT bridges this gap by integrating structures that allow test equipment to probe, control, and observe internal states efficiently.

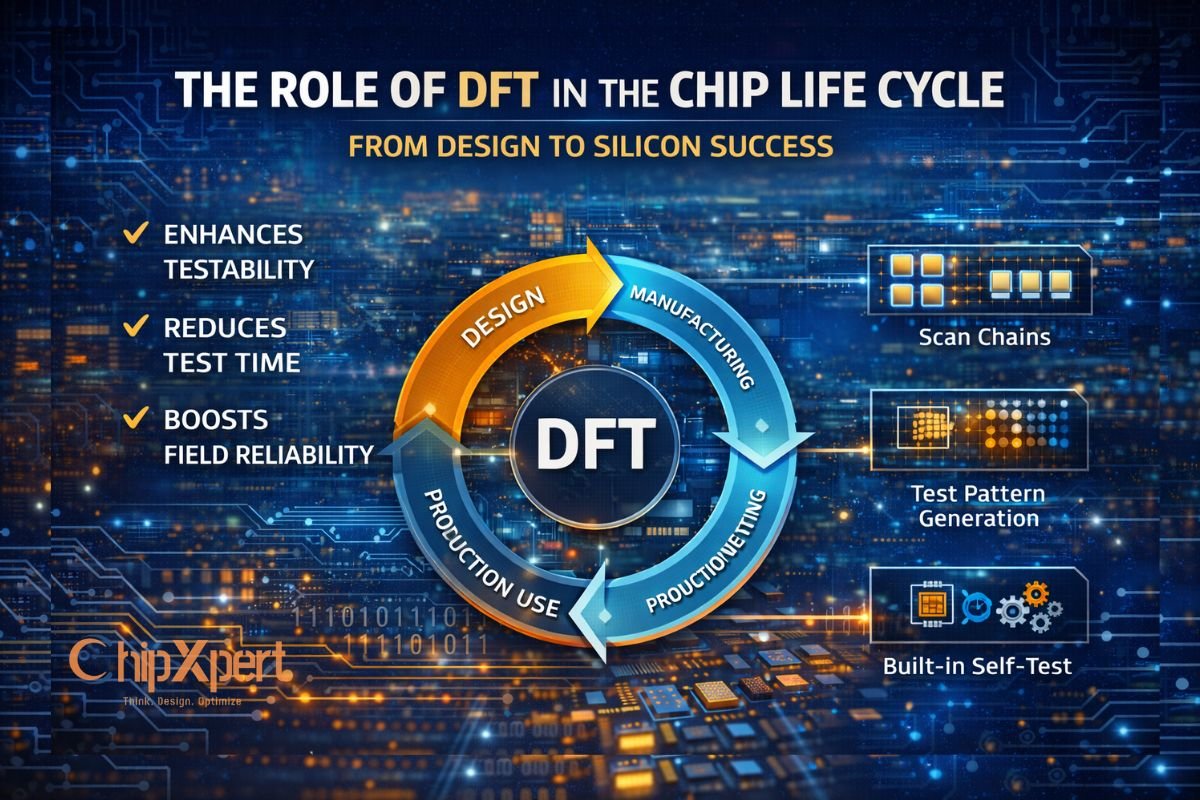

How DFT Fits into the Chip Life Cycle

The journey of a chip from idea to product can be broadly divided into several stages:

- Architecture and Specification

- Functional Design

- Synthesis and Implementation

- Verification

- DFT Insertion

- Manufacturing Test

- Production and Field Operation

DFT plays a role not just at one stage, but across multiple phases of this life cycle.

DFT During Design and Implementation

In the early phases, designers should plan for DFT alongside functional logic. Waiting until the end to insert test structures can lead to mismatches, greater design costs, and compromised coverage.

Inserting DFT at the right stage ensures:

- Better observability : the ability to check internal signals

- Improved controllability : the ability to set internal nodes to known states

- Minimal impact on performance and area

Common techniques applied at this stage include scan chains and test compression logic.

Scan Chains: The Backbone of Chip Testability

Scan chains are one of the most widely used DFT techniques. They connect flip-flops and storage elements in a way that allows external test patterns to shift data in and out of internal registers.

Instead of trying to stimulate internal nodes through just functional inputs (which is slow and inefficient), scan chains allow:

- Fast loading of test vectors

- Observation of internal state directly

- Simplified detection of defects

In short, scan chains transform difficult internal test points into manageable interfaces for automated test equipment (ATE).

Test Pattern Generation and Fault Coverage

Once DFT structures like scan chains are in place, automated tools generate test patterns that map to potential failure modes in the physical design.

A good DFT strategy aims for high fault coverage — meaning most likely defects are exercised by test patterns. These defects include:

- Stuck-at faults

- Transition faults

- Bridging faults

High coverage ensures that manufacturing defects are caught early, reducing the risk of faulty chips slipping into production.

Built-In Self-Test (BIST) for On-Chip Validation

Another powerful DFT methodology is Built-In Self-Test (BIST), where the chip contains its own test logic.

Instead of relying exclusively on external test equipment, BIST allows parts of the chip to:

- Generate test patterns internally

- Perform self-diagnosis

- Report results through dedicated outputs

Memory BIST (MBIST) and Logic BIST are typical examples, especially useful for large memory blocks and critical logic where external test access is limited.

DFT and Manufacturing Test

After physical design and fabrication, DFT becomes essential in manufacturing test — the stage where chips are validated before shipping.

Manufacturers use the DFT infrastructure to:

- Load test patterns efficiently

- Measure responses

- Detect defects caused by manufacturing variations

Without DFT, this test process would be much slower, less thorough, and far more expensive.

DFT’s Impact on Time-to-Market

In a competitive chip market, reducing development and validation time can make the difference between success and delay.

A strong DFT strategy accelerates:

- Test pattern generation

- Fault detection

- Debug cycles

- Yield analysis

Because issues are caught early and exhaustively, fewer iterations are required before tape-out and production.

DFT and Field Reliability

DFT doesn’t just help in manufacturing, it also improves field reliability.

By enabling thorough testing before chips leave the factory, it reduces the likelihood of defects showing up in real-world use. This leads to:

- Longer product lifetimes

- Higher customer satisfaction

- Reduced warranty costs

For safety-critical applications like automotive or medical devices, DFT isn’t optional, it’s fundamental.

Choosing a Smart DFT Strategy

Implementing DFT is not one-size-fits-all. Effective DFT planning depends on:

- Design complexity

- Target applications

- Performance and area constraints

- Test goals (coverage vs. cost)

Early collaboration between design, verification, and test teams yields the best outcomes.

A thoughtful DFT plan balances high coverage with minimal overhead, ensuring that the chip performs well without unnecessary test structures bloating the design.

Conclusion: DFT — A Foundation for Quality and Success

In the chip development life cycle, DFT is not a minor add-on, it’s a foundational element that affects manufacturability, reliability, and overall product success.

From enabling efficient internal access through scan chains, to reducing test time via BIST, and improving production quality through high fault coverage, DFT empowers teams to deliver reliable and robust silicon at scale.

For modern VLSI engineers, mastering DFT concepts and their application is a valuable skill, one that bridges the gap between good design and real-world chip success.

Share your question in comments or talk to our mentor team for batch guidance.

Need Fee, Duration, or Demo Class Details?

Talk to our admin team for the latest batch plan and career guidance.

Contact Admin TeamAsk the Admin Team

Drop your basic question in comments: eligibility, prerequisites, tools, fee range, and placement support.

Our team reviews and responds regularly.